Board:asus/kgpe-d16: Difference between revisions

No edit summary |

mNo edit summary |

||

| Line 12: | Line 12: | ||

Incidentally, this design places the IOMMU, which is part of the SR5690, in the correct location to properly shield the main CPU from all unauthorized traffic. If the southbridge connected directly to a HyperTransport link there would be no way to prevent unauthorized DMA from legacy PCI devices connected to the southbridge, or even from the southbridge's embedded microprocessor. | Incidentally, this design places the IOMMU, which is part of the SR5690, in the correct location to properly shield the main CPU from all unauthorized traffic. If the southbridge connected directly to a HyperTransport link there would be no way to prevent unauthorized DMA from legacy PCI devices connected to the southbridge, or even from the southbridge's embedded microprocessor. | ||

== | == Installation notes == | ||

* coreboot must be flashed externally when migrating from the proprietary BIOS. After coreboot has been flashed and booted at least once, flashrom can safely reprogram the ROM under Linux. | * coreboot must be flashed externally when migrating from the proprietary BIOS. After coreboot has been flashed and booted at least once, flashrom can safely reprogram the ROM under Linux. | ||

* When migrating from the proprietary BIOS, after flashing coreboot the CMOS memory *must* be cleared. Failing to clear the CMOS will typically result in odd hangs during the boot process. | * When migrating from the proprietary BIOS, after flashing coreboot the CMOS memory *must* be cleared. Failing to clear the CMOS will typically result in odd hangs during the boot process. | ||

Revision as of 23:50, 3 March 2016

To boot with a second CPU package installed the extra (disconnected) 12V EPS connector MUST be connected to a 4-pin power source.

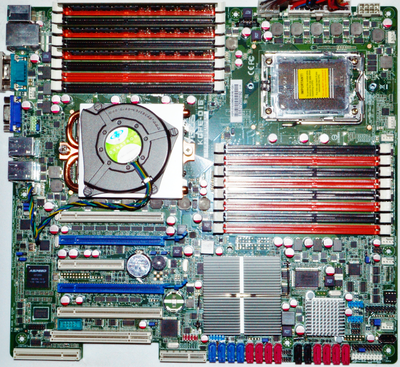

The KGPE-D16 is a relatively modern AMD Family 10h / 15h motherboard. It is well supported and stable under Coreboot, with all CPUs, RAM, and peripherals functioning normally. Family 10h processors do not currently support the isochronous mode required to enable the IOMMU, but Family 15h processors work well with the IOMMU enabled.

This board is automatically tested by Raptor Engineering's test stand. For more details please visit AutoTest/RaptorEngineering.

A basic system diagram is available in the official manual, which can be downloaded from ASUS directly or from [Puget Systems]. The diagram is available in Appendix A.1 and has been confirmed to match the hardware shipping from ASUS. Not indicated are the PCIe lane widths for the gigabit network controller, which are both x1. All legacy PCI devices share the same bus, and partially due to this design the SP5100 has severe issues with bridging high-bandwidth PCI peripherals. As such, an external PCI-PCIe bridge is recommended should you need to interface a high bandwidth legacy PCI device to this system; ASMedia controllers have been verified to function correctly.

Northbridge functions are distributed between the CPU internal northbridge and the SR5690 northbridge, which is effectively a HyperTransport to ALink/PCIe translator and switch. There is a separate SP5100 southbridge device, adjacent to the northbridge and residing under the smaller heatsink of the two. This device provides all traditional southbridge services including the LPC bridge and SATA controllers. All southbridge-destined messages, including CPU-originated power state control messages over HyperTransport, pass through the CPU northbridge and are routed to the southbridge via the SR5690 northbridge device.

Incidentally, this design places the IOMMU, which is part of the SR5690, in the correct location to properly shield the main CPU from all unauthorized traffic. If the southbridge connected directly to a HyperTransport link there would be no way to prevent unauthorized DMA from legacy PCI devices connected to the southbridge, or even from the southbridge's embedded microprocessor.

Installation notes

- coreboot must be flashed externally when migrating from the proprietary BIOS. After coreboot has been flashed and booted at least once, flashrom can safely reprogram the ROM under Linux.

- When migrating from the proprietary BIOS, after flashing coreboot the CMOS memory *must* be cleared. Failing to clear the CMOS will typically result in odd hangs during the boot process.

Known issues

- GRUB appears to have USB interrupt issues under both Libreboot and coreboot. This typically manifests as very slow boot / slow typing on USB keyboards. This issue appears to extend to the KCMA-D8 and KFSN4-DRE boards as well. SeaBIOS is not affected by this issue.