Board:asus/kgpe-d16

The wiki is being retired!

Documentation is now handled by the same processes we use for code: Add something to the Documentation/ directory in the coreboot repo, and it will be rendered to https://doc.coreboot.org/. Contributions welcome!

To boot with a second CPU package installed the extra (disconnected) 12V EPS connector MUST be connected to a 4-pin power source.

General Information

The KGPE-D16 is a relatively modern AMD Family 10h / 15h motherboard. It is well supported and stable under Coreboot, with all CPUs, RAM, and peripherals functioning normally. Family 10h processors do not currently support the isochronous mode required to enable the IOMMU, but Family 15h processors work well with the IOMMU enabled.

This board is automatically tested by Raptor Engineering's test stand. For more details please visit AutoTest/RaptorEngineering.

A basic system diagram is available in the official manual, which can be downloaded from ASUS directly or from Puget Systems. The diagram is available in Appendix A.1 and has been confirmed to match the hardware shipping from ASUS. Not indicated are the PCIe lane widths for the gigabit network controller, which are both x1. All legacy PCI devices share the same bus, and partially due to this design the SP5100 has severe issues with bridging high-bandwidth PCI peripherals. As such, an external PCI-PCIe bridge is recommended should you need to interface a high bandwidth legacy PCI device to this system; ASMedia controllers have been verified to function correctly.

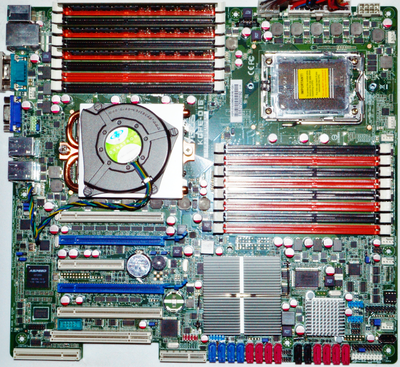

Northbridge functions are distributed between the CPU internal northbridge and the SR5690 northbridge, which is effectively a HyperTransport to ALink/PCIe translator and switch. There is a separate SP5100 southbridge device, adjacent to the northbridge and residing under the smaller heatsink of the two. This device provides all traditional southbridge services including the LPC bridge and SATA controllers. All southbridge-destined messages, including CPU-originated power state control messages over HyperTransport, pass through the CPU northbridge and are routed to the southbridge via the SR5690 northbridge device.

Incidentally, this design places the IOMMU, which is part of the SR5690, in the correct location to properly shield the main CPU from all unauthorized traffic. If the southbridge connected directly to a HyperTransport link there would be no way to prevent unauthorized DMA from legacy PCI devices connected to the southbridge, or even from the southbridge's embedded microprocessor.

Installation Notes

- coreboot must be flashed externally when migrating from the proprietary BIOS. After coreboot has been flashed and booted at least once, flashrom can safely reprogram the ROM under Linux.

- When migrating from the proprietary BIOS, after flashing coreboot the CMOS memory *must* be cleared. Failing to clear the CMOS will typically result in odd hangs during the boot process.

RAM HCL

The following RAM models and configurations have been tested by either Raptor Engineering or a third party and are know to work as of the stated GIT revision. The bolded configuration is automatically tested by Raptor Engineering on every coreboot GIT commit and for most relevant Gerrit changesets; please see the board-status repository for the latest tested GIT hash.

| Manufacturer | Model | Size | Speed | Type | ECC | Populated Slots | CPU | Mainboard | Firmware |

|---|---|---|---|---|---|---|---|---|---|

| Micron | 36KSF2G72PZ-1G4E1 | 16GB | DDR3-1333 | Registered | Yes | A2 / C2 | Opteron 6378 | ASUS KGPE-D16 | Coreboot 2268e0d or later |

| Hynix/Hyundai | HMT151R7BFR4C-H9 | 4GB | DDR3-1333 | Registered | Yes | A2 / C2 | Opteron 6276 | ASUS KGPE-D16 | Libreboot 437619c |

| Kingston | 9965525-055.A00LF | 8GB | DDR3-1600 | Unbuffered | Yes | A2 / C2 / E2 / F2 | Opteron 6328 | ASUS KGPE-D16 | Coreboot 9fba481 |

Processor Summary

In addition to the 1 or 2 main CPUs, there are no less than three known secondary processors present on the mainboard. All are disabled when running under coreboot.

- There is a very poorly documented microprocessor inside the SR5690; purpose and type unknown. It is believed this processor requires a firmware upload from the main platform firmware or via JTAG in order to start execution.

- A single 8051 processor core is present inside the SB700 southbridge. It normally handles errata related to power states and may also be responsible for the blinking power LED in S3 suspend under the proprietary BIOS. It is believed accesses made by this processor are responsible for the flashrom write failure when the board is booted from the proprietary BIOS. This processor also requires a firmware upload from the main platform firmware or via JTAG in order to start execution.

- The BMC has an integrated ARM core. This is disabled by pin strap when the BMC firmware module is not installed.

Some processors may be present on or activated by add-on modules:

- The optional PIKE add-on cards use ARM cores to handle the SAS protocol, though this firmware is directly loaded from a Flash chip on the module and does not involve any non-local components (e.g. the main CPU never touches the firmware on these modules outside of a manual reflash operation). Raptor Engineering is currently unaware of any SAS controllers that operate without a secondary processor or use libre firmware; the protocol is simply too complex to handle via a mask ROM, and as there are only one or two suppliers of SAS controllers there is very little incentive to release the source code to the firmware. Writing a libre firmware to replace the existing firmware may technically be possible, however it is extremely unlikely this will ever happen due to the man-decades required.

- Installing an ASUS iKVM firmware module will activate the ARM core in the BMC, which has full system access to all peripherals and possibly memory. It is not recommended to use this module as the firmware is both highly privileged and proprietary, and is known to contain at least one critical security bug. Raptor Engineering is willing to port OpenBMC to this board under contract; please contact us if you are interested.

Known Issues

- The EHCI debug console causes severe USB problems under both Libreboot and coreboot. This typically manifests as very slow boot / slow typing on USB keyboards. This issue appears to extend to the KCMA-D8 and KFSN4-DRE boards as well.

Certain DIMMs do not reliably train, leading to slow startup or a reboot loop. The majority of tested DIMMs function normally, however.Fixed as of coreboot GIT hash 8b9c807 (04/22/2016)RDIMMs do not function on the second slot of a channel (black slots).Fixed as of coreboot GIT hash 2bb1d30 (04/30/2016)- Certain hardware revisions of these mainboards appear to contain a bug that leads to a hang in ramstage after cold start, with a varying probability dependent on unknown factors potentially including the debug level, debug output device, and binary Flash layout. Non-affected boards appear to generate an MCE and restart instead of hanging. The hang and/or MCE also appears to be dependent on CPU frequency, with slower CPUs such as the Opteron 6262HE more likely to generate the hang. It is possible, though not confirmed, that the hang is due to generation of an MCE while the SB700 and attached LPC devices are being reconfigured; if this is the case, this would be an unfortunate instance of a hardware bug exposed by coreboot's relatively fast startup.

- Certain models and populations of DIMMs do not function under either coreboot or the proprietary BIOS. These failures may also be contingent on the exact PCB revision and / or CPU model installed. For a list of known failing combinations please visit KGPE-D16 Known Bad Configurations.