Board:gigabyte/m57sli: Difference between revisions

m (→Status: Cosmetics and updates.) |

|||

| (361 intermediate revisions by 9 users not shown) | |||

| Line 1: | Line 1: | ||

This is [[end of life]] hardware, if you wish to get one you probably have to buy them used. However, the unique with this board is that it has high Coreboot [[Gigabyte m57sli Vendor Cooperation Score|Vendor Cooperation Score]] (VCS) and ECC memory support that mainly are used for servers. | |||

== Which board do you have? == | == Which board do you have? == | ||

The '''GIGABYTE GA-M57SLI-S4''' seems to exist in 3 versions according to the link in https://github.com/coreboot/coreboot/blob/master/src/mainboard/gigabyte/m57sli/board_info.txt. | |||

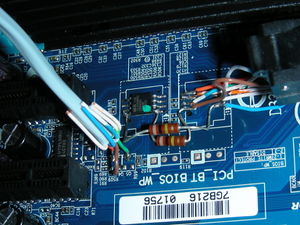

revision 1.0, and 1.1, are supplied with PLCC32 ([http://www.gigabyte.com/products/product-page.aspx?pid=2539#ov soldered BIOS]) and revision 2.0 with single 8 pin SOIC (SPI). All board revisions have unpopulated secondary pads. For the PLCC32 versions, the procedure outlined below can be used to add a ROM socket. | |||

{| | {| | ||

| Line 11: | Line 10: | ||

| [[Image:m57slis4-spi.jpg|thumb|An SPI revision of the GA-M57SLI-S4]] | | [[Image:m57slis4-spi.jpg|thumb|An SPI revision of the GA-M57SLI-S4]] | ||

|} | |} | ||

There is a version with a PLCC socket for the BIOS chip ([http://www.motherboards.org/imageview.html?i=/images/reviews/motherboards/1628_p6_6.jpg socketed BIOS]), but this might be a pre-production board since nobody has so far (2007/03) confirmed the purchase of a GA-M57SLI-S4 board with socketed BIOS. The mainboard photo on the backside of the GA-M57SLI-S4 box shows a ROM socket too. | |||

There are 2 recent legacy BIOS variants are (for fallback purposes): | |||

* F15E | |||

** F15E for GA-M57SLI-S4 (rev. 1.0) non AM3, plcc (fifth variant: socketed plcc, maybe on early sample board only) | |||

** F15E for GA-M57SLI-S4 (rev. 1.1) non AM3, plcc (not flashable with legacy tool here (no 'chipset support') | |||

* FHL for GA-M57SLI-S4 (rev. 2.0) AM3 ready, soic | |||

== Status == | == Status == | ||

| Line 17: | Line 25: | ||

|CPU_status = OK | |CPU_status = OK | ||

| | |CPU_L1_status = OK | ||

|CPU_L2_status = OK | |||

| | |CPU_L3_status = N/A | ||

| | |CPU_multiple_status = N/A | ||

|CPU_multicore_status = OK | |||

|CPU_virt_status = OK | |||

|CPU_virt_comments = tested with the kvm package of ubuntu 7.04 | |||

|RAM_EDO_status = N/A | |||

|RAM_SDRAM_status = N/A | |||

|RAM_SODIMM_status = N/A | |||

|RAM_DDR_status = N/A | |||

|RAM_DDR2_status = OK | |||

|RAM_DDR3_status = N/A | |||

|RAM_dualchannel_status = OK | |RAM_dualchannel_status = OK | ||

|RAM_dualchannel_comments = According to memtest86+ it works. | |RAM_dualchannel_comments = According to memtest86+ it works. | ||

|RAM_ecc_status = Untested | |||

|IDE_status = OK | |IDE_status = OK | ||

|IDE_25_status = N/A | |IDE_25_status = N/A | ||

|IDE_CF_status = OK | |IDE_CF_status = OK | ||

|IDE_CF_comments = Tested with an CF-IDE adapter without DMA support. Booting with | |IDE_CF_comments = Tested with an CF-IDE adapter without DMA support. Booting with coreboot is no problem. Booting with propritary BIOS didn't work. | ||

|CDROM_DVD_status = OK | |||

| | |||

|SATA_status = OK | |SATA_status = OK | ||

|SATA_comments = A FILO patch is needed (see below) as | |SATA_comments = A FILO patch is needed (see below) as coreboot is too fast and the disks have not spun up yet when coreboot is done. | ||

|USB_status = OK | |USB_status = OK | ||

|USB_comments = Tested: mounting USB storage devices and accessing files on them. USB MIDI-keyboard works, too (keyboard == the music instrument, in this case). | |USB_comments = Tested: mounting USB storage devices and accessing files on them. USB MIDI-keyboard works, too (keyboard == the music instrument, in this case). | ||

|Onboard_VGA_status = N/A | |Onboard_VGA_status = N/A | ||

|Onboard_ethernet_status = OK | |Onboard_ethernet_status = OK | ||

|Onboard_audio_status = OK | |Onboard_audio_status = OK | ||

|Onboard_audio_comments = Use '''modprobe snd-hda-intel''' (Alsa). | |Onboard_audio_comments = Use '''modprobe snd-hda-intel''' (Alsa). | ||

|Onboard_modem_status = N/A | |||

|Onboard_firewire_status = OK | |||

|Onboard_firewire_comments = Confirmed working as of r3023 - a firewire disk is detected and works fine. | |||

|Smartcard_status = N/A | |||

|Onboard_CF_status = N/A | |||

|Onboard_PCMCIA_status = N/A | |||

|Onboard_SCSI_status = N/A | |||

|PCI_cards_status = | |AMR_cards_status = N/A | ||

|PCI_cards_comments = | |ISA_cards_status = N/A | ||

|PCI_cards_status = OK | |||

| | |PCI_cards_comments = Works on hardware rev.2. Needs coreboot v2 >= r4362. Please do additional tests on hardware rev.1. | ||

| | |Mini_PCI_cards_status = N/A | ||

|AGP_cards_status = N/A | |||

|PCIX_cards_status = N/A | |||

|PCIE_x1_status = OK | |||

|PCIE_x1_comments = Works on hardware rev.2. Needs coreboot v2 >= r4362. Please do additional tests on hardware rev.1. | |||

|PCIE_x2_status = N/A | |||

|PCIE_x4_status = N/A | |||

|PCIE_x8_status = N/A | |||

|PCIE_x16_status = OK | |||

|PCIE_x16_comments = Works on hardware rev.2. Needs coreboot v2 >= r4362. Please do additional tests on hardware rev.1. | |||

|PCIE_x32_status = N/A | |||

|HTX_status = N/A | |HTX_status = N/A | ||

|Floppy_status = Untested | |||

|Floppy_comments = Should work, but '''***needs testing***'''. | |||

|COM1_status = OK | |COM1_status = OK | ||

|COM1_comments = Serial console for | |COM1_comments = Serial console for coreboot and Linux is fully operational. | ||

|COM2_status = N/A | |COM2_status = N/A | ||

|PP_status = OK | |||

|PP_comments = Works with a parallel port printer. (Needs coreboot v2 >= r4396.) | |||

|PP_status = | |||

|PP_comments = | |||

|PS2_keyboard_status = OK | |PS2_keyboard_status = OK | ||

|PS2_keyboard_comments = | |PS2_keyboard_comments = Works on Seabios without problems. | ||

|PS2_mouse_status = OK | |PS2_mouse_status = OK | ||

| | |Game_port_status = N/A | ||

|IR_status = N/A | |||

| | |||

|Speaker_status = OK | |Speaker_status = OK | ||

|Speaker_comments = Works with '''beep''' (use '''modprobe pcspkr'''). | |Speaker_comments = Works with '''beep''' (use '''modprobe pcspkr'''). | ||

|DiskOnChip_status = N/A | |||

|CPUfreq_status = | |Sensors_status = OK | ||

|CPUfreq_comments = | |Sensors_comments = Sensors and fans work, see [http://coreboot.org/pipermail/coreboot/2007-April/020307.html instructions]. Some sensor readouts are off, and the pwm polarity seems to be inverted, but fan speed can be set. | ||

|Watchdog_status = OK | |||

|Watchdog_comments = modprobe it87_wdt | |||

|CAN_bus_status = N/A | |||

|SMBus_status = OK | |||

|CPUfreq_status = OK | |||

|CPUfreq_comments = Needs coreboot v2 >= r4364. | |||

|Powersave_status = N/A | |||

|ACPI_status = OK | |||

|ACPI_comments = Needs coreboot v2 >= r4364. | |||

|Reboot_status = OK | |||

|Poweroff_status = OK | |||

|Poweroff_comments = Needs coreboot v2 >= r4364. | |||

|LEDs_status = OK | |||

|LEDs_comments = HD-LED works. Power-LED untested. | |||

|HPET_status = OK | |||

|HPET_comments = Needs coreboot v2 >= r4364. | |||

|RNG_status = N/A | |||

|WakeOnModem_status = Untested | |||

|WakeOnLAN_status = Untested | |||

|WakeOnKeyboard_status =Untested | |||

|WakeOnMouse_status = Untested | |||

|Flashrom_status = OK | |||

|Flashrom_comments = Use revision 3088 or higher. [[Flashrom]] now works on both the PLCC and SOIC/SPI versions of the board. | |||

}} | |||

=== Supported CPUs === | |||

====Factory BIOS CPU support lists==== | |||

** [http://www.gigabyte.com/support-downloads/cpu-support-popup.aspx?pid=2539 GA-M57SLI-S4 2.0] | |||

** [http://www.gigabyte.com/support-downloads/cpu-support-popup.aspx?pid=2383 GA-M57SLI-S4 1.1] | |||

** [http://www.gigabyte.com/support-downloads/cpu-support-popup.aspx?pid=2287 GA-M57SLI-S4 1.0] | |||

====Coreboot CPU support list==== | |||

<div style="color: red">"(Note) If you install an AMD AM3/AM2+ CPU on AM2 motherboard, the system bus speed will downgrade from HT3.0(5200 MT/s) to HT1.0 (2000 MT/s); however, the frequency of AM2+ CPU will not be impacted." - GIGABYTE</div> | |||

Initial socket CPUs are listed as they work with any factory BIOS version, are likely to work with Coreboot, are affordable, and AMD CPUs are sometimes unlocked in early editions. Also, if you plan to evaluate a series of CPUs, please think about buying a CPU cooler compatible for respectively sockets. | |||

| | {| class="wikitable sortable" border="1" style="font-size:smaller" | ||

| | |- | ||

! rowspan="2" style="background: gray" | Date | |||

! colspan="2" style="background: lightyellow" | Mainboard | |||

! colspan="12" style="background: lightgreen" | CPU | |||

! colspan="5" style="background: lightblue" | Coreboot | |||

! | |||

|- | |||

! style="background: lightyellow" | Model | |||

! style="background: lightyellow" | PCB | |||

! style="background: lightgreen" | Backward compatibility and/or unique feature | |||

! style="background: lightgreen" | CPUID signature | |||

! style="background: lightgreen" | Family | |||

! style="background: lightgreen" | Frequency | |||

! style="background: lightgreen" | Processor name (BIOS) | |||

! style="background: lightgreen" | Part number(s) | |||

! style="background: lightgreen" | Introduction date | |||

! style="background: lightgreen" | Socket(s) | |||

! style="background: lightgreen" | Microarchitecture | |||

! style="background: lightgreen" | Model | |||

! style="background: lightgreen" | Stepping | |||

! style="background: lightgreen" | TDP | |||

! style="background: lightblue" | Version | |||

! style="background: lightblue" | Git clone revision | |||

! style="background: lightblue" | Working with on-board VGA | |||

! style="background: lightblue" | Working with off-board VGA | |||

! style="background: lightblue" | Working overclocked (ACC) | |||

|- | |||

| 2015-01-29 | |||

| M57SLI-S4 | |||

| 2.0 | |||

| style="border-style: solid; border-width: 4px; border-color: purple" | First choice CPU for Coreboot evaluation (if this one runs you can try other models): Boards lowest supported CPU (of all CPUs, K8 family, AM2 socket) | |||

| [http://www.cpu-world.com/CPUs/K8/AMD-Sempron%2064%202800+%20-%20SDA2800IAA2CN%20%28SDA2800CNBOX%29.html 40FF2] | |||

| AMD Sempron | |||

| 2800+ (rated)<br />1600 MHz (real) | |||

| AMD Sempron(tm) Processor 2800+ | |||

| SDA2800IAA2CN is an OEM/tray microprocessor<br />SDA2800CNBOX is a boxed microprocessor | |||

| 2006-05-23 | |||

| AM2 | |||

| K8/15 (0Fh) | |||

| 79 (04Fh) | |||

| F2 | |||

| 62W | |||

| 4.0-8014-g20c2c4b | |||

| 20c2c4b277e72c279229c1eea19aeaee94ab2ae1 | |||

| N/A | |||

| {{no|No}} | |||

| {{no|Untested}} | |||

|- | |||

| - | |||

| M57SLI-S4 | |||

| 2.0 | |||

| Boards lowest supported CPU for K10.5 family, and AM2+ socket | |||

| [http://www.cpu-world.com/CPUs/K10/AMD-Athlon%20X2%207450%20-%20AD7450WCJ2BGH.html 0F23h] | |||

| AMD Athlon | |||

| 2400 MHz | |||

| AMD Athlon(tm) 7450 Dual-Core Processor | |||

| AD7450WCJ2BGH is an OEM/tray microprocessor | |||

| 2008-12-14 | |||

| AM2, AM2+ | |||

| K10.5/16 (010h) | |||

| 2 (02h) | |||

| B3 | |||

| 95W | |||

| 4.0-7922-g78c5d58 | |||

| 78c5d584a087265e44b076647db19efd4db4a7bb | |||

| N/A | |||

| {{no|Untested}} | |||

| - | |||

|- | |||

| - | |||

| M57SLI-S4 | |||

| 2.0 | |||

| Boards lowest supported AM3 socket CPU | |||

| [http://www.cpu-world.com/CPUs/K10/AMD-Sempron%20140%20-%20SDX140HBK13GQ%20%28SDX140HBGQBOX%29.html 100F62] | |||

| AMD Sempron | |||

| 2700 MHz | |||

| AMD Sempron(tm) 140 Processor | |||

| SDX140HBK13GQ is an OEM/tray microprocessor<br />SDX140HBGQBOX is a boxed microprocessor | |||

| 2009-07-22 | |||

| AM2+, AM3 | |||

| K10.5/16 (010h) | |||

| 6 (06h) | |||

| C2 | |||

| 45W | |||

| 4.0-7922-g78c5d58 | |||

| 78c5d584a087265e44b076647db19efd4db4a7bb | |||

| N/A | |||

| {{no|Untested}} | |||

| - | |||

|- | |||

| - | |||

| M57SLI-S4 | |||

| 2.0 | |||

| Boards only Opteron supported CPU. Note that the board also has ECC support; Opteron with ECC memory are used in servers. | |||

| [http://www.cpu-world.com/CPUs/K8/AMD-Second%20Generation%20Opteron%201210%20-%20OSA1210IAA6CZ%20%28OSA1210CZBOX%29.html 40F33] | |||

| AMD Second Generation Opteron | |||

| 1800 MHz | |||

| Dual-Core AMD Opteron(tm) Processor 1210 | |||

| OSA1210IAA6CZ is an OEM/tray microprocessor<br />OSA1210CZBOX is a boxed microprocessor | |||

| 2006-08-15 | |||

| AM2 | |||

| K8/15 (0Fh) | |||

| 67 (043h) | |||

| F3 | |||

| 103W | |||

| 4.0-7922-g78c5d58 | |||

| 78c5d584a087265e44b076647db19efd4db4a7bb | |||

| N/A | |||

| {{no|Untested}} | |||

| - | |||

|- | |||

| - | |||

| M57SLI-S4 | |||

| 2.0 | |||

| Boards lowest supported Phenom CPU | |||

| [http://www.cpu-world.com/CPUs/K10/AMD-Phenom%20X3%208250e%20-%20HD8250ODJ3BGH%20%28HD8250ODGHBOX%29.html 100F23] | |||

| AMD Phenom X3 | |||

| 1900 MHz | |||

| AMD Phenom(tm) 8250e Triple-Core Processor | |||

| HD8250ODJ3BGH is an OEM/tray microprocessor<br />HD8250ODGHBOX is a boxed microprocessor | |||

| 2008-09-08 | |||

| AM2+ / AM3 | |||

| K10.5/16 (010h) | |||

| 2 (02h) | |||

| B3 | |||

| 65W | |||

| 4.0-7922-g78c5d58 | |||

| 78c5d584a087265e44b076647db19efd4db4a7bb | |||

| N/A | |||

| {{no|Untested}} | |||

| - | |||

|- | |||

| 2015-01-10 | |||

| M57SLI-S4 | |||

| 2.0 | |||

| - | |||

| [http://www.cpu-world.com/CPUs/K8/AMD-Athlon%2064%20X2%204600%2B%20-%20ADO4600IAA5CZ%20%28ADO4600CZBOX%29.html 40F33] | |||

| AMD Athlon 64 X2 | |||

| 4600+ (rated)<br />2400 MHz (real) | |||

| AMD Athlon(tm) 64 X2 Dual Core Processor 4600+ | |||

| ADO4600IAA5CZ is an OEM/tray microprocessor<br />ADO4600CZBOX is a boxed microprocessor | |||

| 2006-05-23 | |||

| AM2 | |||

| K8/15 (0Fh) | |||

| 67 (043h) | |||

| F3 | |||

| 65W | |||

| 4.0-7922-g78c5d58 | |||

| 78c5d584a087265e44b076647db19efd4db4a7bb | |||

| N/A | |||

| {{no}} | |||

| {{no|Untested}} | |||

|} | |||

| | * '''Motherboard''' | ||

** '''Model''': with lshw: <code>sudo lshw -short | grep bus</code> | |||

* '''CPU''': Data used to figure out unique CPU in the [http://www.cpu-world.com/cgi-bin/CPUID.pl CPUID database] or factory BIOS supported CPUs. This is useful method to find out the CPU '''Part number(s)''' for an already running computer as it is written on the CPU normally blocked by a cooler. | |||

| | ** '''Family''': With dmidecode: <code>sudo dmidecode -s processor-manufacturer && sudo dmidecode -s processor-family</code>. In CPUID database search ''Family''. | ||

** '''Introduction date''': In CPUID database search ''Introduction date''. | |||

** '''Microarchitecture''' (''CPU family'', ''CPU architecture''): In /proc/cpuinfo search ''cpu family''. In CPUID database search ''Family''. | |||

| | ** '''Frequency''': With dmidecode: <code>sudo dmidecode | grep "Current Speed"</code>. In CPUID database search ''Frequency''. | ||

** '''Processor name (BIOS)''' (''CPU name string''): In /proc/cpuinfo search ''model name''. In CPUID database search ''Processor name (BIOS)'' or ''CPU name string''. | |||

** '''Socket''' (''CPU socket''): With dmidecode: <code>sudo dmidecode | grep Socket</code>. In CPUID database search ''Socket''. | |||

** '''Model''': In /proc/cpuinfo search ''model''. In CPUID database search ''Model''. | |||

** Vendor CPU Support List data. Used to alocate the CPU on their list. | |||

*** '''Stepping''' (''Stepping level'', ''CPU stepping''): The term stepping level in the context of CPU architecture is a version/revision number. In [[#Factory BIOS CPU support lists|Factory BIOS CPU support lists]] search ''Stepping''. In /proc/cpuinfo search ''stepping''. In CPUID database search ''Core stepping''. | |||

*** '''TDP''' (''Thermal Design Power'', ''Wattage''): In [[#Factory BIOS CPU support lists|Factory BIOS CPU support lists]] search ''Wattage''. In CPUID database search ''Watt''. | |||

* '''Factory BIOS''' | |||

** '''Version''': With dmidecode: <code>sudo dmidecode -s bios-version</code> | |||

* '''Coreboot''' | |||

** '''Version''': <code>git describe --tags</code> | |||

** '''Git clone revision''': <code>git log -1 --format=%H</code> | |||

** '''Working overclocked (ACC)''': Advanced clock calibration (ACC) is a feature originally available for Phenom families of processors, particularly for Black Edition ones, to increase the overclocking potential of the CPU. ACC is supported by the SB710 and the SB750 southbridges, and available through BIOS settings on some motherboards. (Disclaimer - overclocking may damage your CPU. Damage, caused by overclocking, is not covered by CPU warranty.) See [http://www.amdgeeks.net/overclockdatabase AMDGeeks Overclock database] for CPUs. | |||

== Before you begin == | == Before you begin == | ||

The fact that the BIOS is soldered onto the board complicates matters considerably, because it means that one flash of a faulty image will render your board unusable (it will be 'bricked'). [[Top Hat Flash]] does not work with the SST 49LF040B 33-4C-NHE soldered onto the GA-M57SLI-S4, but might work with other chips (FWH). This means a hardware hack is necessary to prevent accidental bricking of the board. | The fact that the BIOS is soldered onto the board complicates matters considerably, because it means that one flash of a faulty image will render your board unusable (it will be 'bricked'). [[Developer Manual/Tools#Top_Hat_Flash|Top Hat Flash]] does not work with the SST 49LF040B 33-4C-NHE soldered onto the GA-M57SLI-S4, but might work with other chips (FWH). This means a hardware hack is necessary to prevent accidental bricking of the board. | ||

With it's standard F8 legacy BIOS it requires the '''noapic''' boot parameter with most old kernels (legacy BIOS v. F12 is better). | |||

This | <div style="color: red">If you're going to work on this board, you need a backup plan in the event you flash a faulty BIOS image. | ||

For example, the [[Developer_Manual/Tools#In_case_of_extra_soldered_BIOS_chip|secondary chip must have different size]] (preferable greater capacity) than the 4 Mbit (512 kB) primary chip (factory chip) in order to avoid accidents: flashrom will not burn the Coreboot image (<code>sudo flashrom -p internal -w Coreboot_4.0-8014-g20c2c4b--Mainboard--Vendor_GIGABYTE._Model_GA-M57SLI-S4._ROM_chip_size_2048KB.rom [...] Error: Image size doesn't match</code>) if the size of the hardware chip mismatch the Coreboot image configured ''ROM chip size''. This is a good thing as it will save you from accidentally burning Cooreboot to the primary chip if you forget to toggle the hardware switch to the secondary chip. Chips with equal size will likely make you break the board one day. You have been warned!</div> | |||

=== Hardware hack === | |||

=== PLCC32 | ==== PLCC32 ==== | ||

If you have a PLCC32 revision, it is possible to desolder the BIOS chip, and replace it with a PLCC socket. You will need some tools (heat gun/pencil, good soldering iron, etc) and soldering experience to do that. The other option is to add a PLCC socket to the empty position next to the soldered-on BIOS chip. With an extra resistor and a switch, this allows switching between 2 BIOS chips. This has been documented carefully by ST; see his [http://private.vlsi.informatik.tu-darmstadt.de/st/instructions.html instructions]. | If you have a PLCC32 revision, it is possible to desolder the BIOS chip, and replace it with a PLCC socket. You will need some tools (heat gun/pencil, good soldering iron, etc) and soldering experience to do that. The other option is to add a PLCC socket to the empty position next to the soldered-on BIOS chip. With an extra resistor and a switch, this allows switching between 2 BIOS chips. This has been documented carefully by ST; see his [http://private.vlsi.informatik.tu-darmstadt.de/st/instructions.html instructions]. | ||

| Line 137: | Line 330: | ||

shops, they do this sort of thing (and more advanced things) all day and should be able to help you for around $50 if you bring the needed components (PLCC socket, resistor, wire and switch). Possibly a friendly TV or radio repair shop could help too, but they may not have suitable soldering equipment for the surface mount parts. | shops, they do this sort of thing (and more advanced things) all day and should be able to help you for around $50 if you bring the needed components (PLCC socket, resistor, wire and switch). Possibly a friendly TV or radio repair shop could help too, but they may not have suitable soldering equipment for the surface mount parts. | ||

Once you put a socket on the board, you will also discover that the [http://www.ioss.com.tw/web/English/RD1BIOSSavior/SelectionChart/PLCCTYPE/RD1PMC4.html RD1-PMC4 BiosSavior] does not work with this motherboard: the RD1's built-in chip seems to be incompatible with the mainboard. This means you will need to hot-swap BIOS chips until you have a working | Once you put a socket on the board, you will also discover that the [http://www.ioss.com.tw/web/English/RD1BIOSSavior/SelectionChart/PLCCTYPE/RD1PMC4.html RD1-PMC4 BiosSavior] does not work with this motherboard: the RD1's built-in chip seems to be incompatible with the mainboard. This means you will need to hot-swap BIOS chips until you have a working coreboot chip. Plugging your BIOS chip into the RD1 and switching it to 'ORG' does work though. I have used the BiosSavior to ease hot swapping; it's a lot easier to pull out the BiosSavior and replace the chip plugged into it than to replace the ROM chip on the board. | ||

This is the list of BiosSavior resellers: [http://www.ioss.com.tw/web/English/WheretoBuy.html IOSS]. | This is the list of BiosSavior resellers: [http://www.ioss.com.tw/web/English/WheretoBuy.html IOSS]. | ||

In the US, FrozenCPU seems to have stock (verified 2007/04). Eksitdata in Sweden also seems to have stock (verified 2007/03). | In the US, FrozenCPU seems to have stock (verified 2007/04). Eksitdata in Sweden also seems to have stock (verified 2007/03). | ||

=== SOIC | ==== SOIC (SPI) ==== | ||

If you have an SOIC revision, you can add a second SOIC chip in the unpopulated position, and use a switch to toggle between both chips. | |||

The most recent instructions by Peter Stuge can be found here [http://stuge.se/m57sli/]. This is the recommended modification. Peter's company also sells pre-modified boards if you don't want to do the soldering, contact peter at stuge dot se for more information. Also, you may watch Peter's video lecture on coreboot available at youtube asf. for recent info. | |||

Older instructions can be found here [http://coreboot.org/pipermail/coreboot/2007-September/024474.html here], and here are [http://stuge.se/lb/m57sli/ some photos]. These instructions have been [http://www.coreboot.org/pipermail/coreboot/2007-October/025906.html confirmed to work]. | |||

It's also possible to put a SOIC socket on the second pad, as [http://www.coreboot.org/pipermail/coreboot/2008-January/028949.html documented by Harald Gutmann], with pictures [http://img141.imageshack.us/img141/8866/dscf1791ob2.jpg here] and [http://img104.imageshack.us/img104/2579/dscf1792nn2.jpg here]. | |||

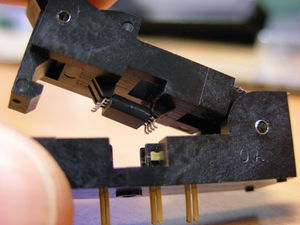

Here's are a few pictures of a completed modification using the older instructions: | |||

{| | |||

| [[Image:M57sli-spi-mod-dscn2921-1024x768.jpg|thumb|SOIC/SPI mod on m57sli]] | |||

| [[Image:Spi-socket-dscn2913-1024x768.jpg|thumb|SOIC/SPI socket with chip, pre installation]] | |||

|} | |||

=== Flashrom === | === Flashrom === | ||

==== PLCC32 chips ==== | |||

Flashrom | Flashrom works fine both under the proprietary BIOS and coreboot. Use revision 3088 or higher. | ||

Flashrom works | ==== SOIC (SPI) chips ==== | ||

Flashrom works well on the SOIC version of the board and can detect various SPI chips, including the factory soldered MX25L4005. | |||

== Payload == | == Payload == | ||

Coreboot requires a [[Payloads|payload]] to boot an operating system. | |||

If you want to boot from the network, you will need to use [http://www.etherboot.org Etherboot]. | If you want to boot from the network, you will need to use [http://www.etherboot.org Etherboot]. | ||

| Line 166: | Line 373: | ||

== Buildrom vs. manual build == | == Buildrom vs. manual build == | ||

You can build a | You can build a coreboot image with a kconfig-style configuration tool ([[buildrom]]) if you want to use FILO or LAB. This is by far the easiest way to build a ROM image. Continue to the [[#Buildrom|Buildrom section]]. | ||

If you want another payload or would like to get closer to the metal, you can use the manual build method outlined below under [[#Manual build|Manual build]]. | If you want another payload or would like to get closer to the metal, you can use the manual build method outlined below under [[#Manual build|Manual build]]. | ||

| Line 176: | Line 383: | ||

Check out buildrom: | Check out buildrom: | ||

svn co svn:// | svn co svn://coreboot.org/buildrom | ||

Now configure buildrom: | Now configure buildrom: | ||

| Line 207: | Line 414: | ||

</pre> | </pre> | ||

Note the root device - FILO sees the first | Note the root device - FILO sees the first SATA device as '''hd4'''. | ||

In order to get serial output from GRUB, you will also need to add something like this to your menu.lst: | In order to get serial output from GRUB, you will also need to add something like this to your menu.lst: | ||

| Line 230: | Line 437: | ||

You will also need a statically linked copy of kexec, which the LAB payload expects to reside at | You will also need a statically linked copy of kexec, which the LAB payload expects to reside at | ||

/ | /kexec on /dev/sda1 | ||

If you are on | If you are on Ubuntu, you can easily recompile your kexec package to be statically linked by following these instructions: | ||

cd /usr/src | cd /usr/src | ||

| Line 249: | Line 456: | ||

dpkg -i kexec-tools_1.101-kdump10-2ubuntu2_i386.deb | dpkg -i kexec-tools_1.101-kdump10-2ubuntu2_i386.deb | ||

Adjust the package name as necessary for your distribution. You can tell if your copy of kexec is statically linked by running 'file' on it: | Adjust the package name as necessary for your distribution. | ||

If you want to build the latest kexec from Debian Sid, you're going to need to be a little more careful. Set -static: | |||

export LDFLAGS="-static" | |||

Then build the package | |||

apt-get source kexec-tools -b | |||

This will fail more or less like this | |||

<pre> | |||

$ gcc -static -lz -o build/sbin/kexec kexec/kexec.o kexec/ifdown.o kexec/kexec-elf.o kexec/kexec-elf-exec.o kexec/kexec-elf-core.o kexec/kexec-elf-rel.o kexec/kexec- elf-boot.o kexec/kexec-iomem.o kexec/crashdump.o kexec/crashdump-xen.o kexec/arch/i386/kexec-x86.o kexec/arch/i386/kexec-elf-x86.o kexec/arch/i386/kexec-elf-rel-x86.o kexec/arch/i386/kexec-bzImage.o kexec/arch/i386/kexec-multiboot-x86.o kexec/arch/i386/kexec-beoboot-x86.o kexec/arch/i386/kexec-nbi.o kexec/arch/i386/x86-linux-setup.o kexec/arch/i386/crashdump-x86.o kexec/purgatory.o libutil.a | |||

kexec/kexec.o: In function `slurp_decompress_file': | |||

/usr/src/kexec-tools-20080324/kexec/kexec.c:503: undefined reference to `gzopen' | |||

/usr/src/kexec-tools-20080324/kexec/kexec.c:519: undefined reference to `gzread' | |||

/usr/src/kexec-tools-20080324/kexec/kexec.c:533: undefined reference to `gzclose' | |||

/usr/src/kexec-tools-20080324/kexec/kexec.c:524: undefined reference to `gzerror' | |||

/usr/src/kexec-tools-20080324/kexec/kexec.c:535: undefined reference to `gzerror' | |||

/usr/src/kexec-tools-20080324/kexec/kexec.c:505: undefined reference to `gzerror' | |||

collect2: ld returned 1 exit status | |||

</pre> | |||

The problem is that the -lz really needs to go at the end of the gcc command line - otherwise it gets filtered out by gcc. When it encounters -lz, it has not yet seen any need for the libz library so it automatically removes it. Manually running | |||

<pre> | |||

gcc -static -o build/sbin/kexec kexec/kexec.o kexec/ifdown.o kexec/kexec-elf.o | |||

kexec/kexec-elf-exec.o kexec/kexec-elf-core.o kexec/kexec-elf-rel.o kexec/kexec-elf-boot.o | |||

kexec/kexec-iomem.o kexec/crashdump.o kexec/crashdump-xen.o kexec/arch/i386/kexec-x86.o | |||

kexec/arch/i386/kexec-elf-x86.o kexec/arch/i386/kexec-elf-rel-x86.o kexec/arch/i386/kexec-bzImage.o | |||

kexec/arch/i386/kexec-multiboot-x86.o kexec/arch/i386/kexec-beoboot-x86.o kexec/arch/i386/kexec-nbi.o | |||

kexec/arch/i386/x86-linux-setup.o kexec/arch/i386/crashdump-x86.o kexec/purgatory.o libutil.a -lz | |||

</pre> | |||

fixes the problem and gives you a static copy of kexec in build/sbin/kexec. | |||

You can tell if your copy of kexec is statically linked by running 'file' on it: | |||

file /sbin/kexec | file /sbin/kexec | ||

| Line 259: | Line 503: | ||

The binary will also be considerably larger than its dynamically linked cousin. | The binary will also be considerably larger than its dynamically linked cousin. | ||

Note that you | Note that you '''must''' build a 32-bit version of kexec, because buildrom puts a 32 bit kernel into the ROM image. A 32-bit kexec can kexec into a 64 bit kernel, so if your system is 64 bit this will work just fine. | ||

The LAB code currently expects lab.conf and kexec to live in / on /dev/sda1. | The LAB code currently expects lab.conf and kexec to live in / on /dev/sda1. | ||

| Line 265: | Line 509: | ||

== Manual build == | == Manual build == | ||

Skip this section if you used buildrom; in that case jump to [[#Burning | Skip this section if you used buildrom; in that case jump to [[#Burning coreboot|Burning coreboot]] below. | ||

=== Building the payload === | === Building the payload === | ||

| Line 332: | Line 576: | ||

terminal --timeout=15 serial console | terminal --timeout=15 serial console | ||

Now execute 'make', which will generate a filo.elf file that will be your payload. You will need to refer to this file to build | Now execute 'make', which will generate a filo.elf file that will be your payload. You will need to refer to this file to build coreboot as explained below, because it gets included in the coreboot ROM image. | ||

=== Your menu.lst entry === | === Your menu.lst entry === | ||

| Line 346: | Line 590: | ||

</pre> | </pre> | ||

Note the root device - FILO sees the first | Note the root device - FILO sees the first SATA device as '''hd4'''. | ||

Also, the GA-M57SLI-S4 will not boot unless you add acpi_use_timer_override as a kernel option - and use a modern kernel (tested on 2.6.20.1 and up). Hopefully this will be fixed in newer kernels. If you have a somewhat older kernel (tested with 2.6.16 and up), add these options: apic=debug acpi_dbg_level=0xffffffff pci=noacpi,routeirq snd-hda-intel.enable_msi=1. | Also, the GA-M57SLI-S4 will not boot unless you add '''acpi_use_timer_override''' as a kernel option - and use a modern kernel (tested on 2.6.20.1 and up). Hopefully this will be fixed in newer kernels. If you have a somewhat older kernel (tested with 2.6.16 and up), add these options: '''apic=debug acpi_dbg_level=0xffffffff pci=noacpi,routeirq snd-hda-intel.enable_msi=1'''. | ||

=== | === Building coreboot === | ||

See the [[Build HOWTO]] for information on how to build coreboot for this board. | |||

== | == Burning coreboot == | ||

Make | Make SURE that you have a fallback position: a ROM chip with backup copy of your factory ROM image (you can make one with [http://flashrom.org flashrom]), and either a socket on the board to plug the backup chip into, or the tools and skills to remove a 'bricked' BIOS chip from the board and replace it with a socket for the backup chip. | ||

If you do not prepare properly, you are likely to brick your motherboard. You have been warned! | |||

You can use flashrom to write the image: | |||

flashrom -p internal -w coreboot.rom | |||

(that's assuming the image is called coreboot.rom). | |||

== Debugging Coreboot execution == | |||

See [[EHCI Debug Port]] for USB debug hardwares that you need to use with the USB debug port. | |||

=== USB debug port === | |||

<pre> | |||

sudo lshw # gives one result for EHCI capable USB port. | |||

*-usb:1 | |||

description: USB controller | |||

product: MCP55 USB Controller | |||

vendor: NVIDIA Corporation | |||

physical id: 2.1 | |||

bus info: pci@0000:00:02.1 | |||

version: a2 | |||

width: 32 bits | |||

clock: 66MHz | |||

capabilities: debug pm ehci bus_master cap_list | |||

configuration: driver=ehci_hcd latency=0 maxlatency=1 mingnt=3 | |||

resources: irq:22 memory:ee204000-ee2040ff | |||

lspci | |||

00:02.1 USB controller: NVIDIA Corporation MCP55 USB Controller (rev a2) | |||

lspci -v | grep ehci | |||

Kernel driver in use: ehci_hcd | |||

lspci -v | |||

00:02.1 USB controller: NVIDIA Corporation MCP55 USB Controller (rev a2) (prog-if 20 [EHCI]) | |||

Subsystem: Gigabyte Technology Co., Ltd Device 5004 | |||

Flags: bus master, 66MHz, fast devsel, latency 0, IRQ 22 | |||

Memory at ee204000 (32-bit, non-prefetchable) [size=256] | |||

Capabilities: <access denied> | |||

Kernel driver in use: ehci_hcd | |||

lspci -nnk | grep 10de:036d | |||

00:02.1 USB controller [0c03]: NVIDIA Corporation MCP55 USB Controller [10de:036d] (rev a2) | |||

</pre> | |||

10de:036d is found on the list of [[EHCI_Debug_Port#Controllers_verified_to_have_the_debug_port_capability|controllers verified to have the debug port capability]] so we know that it is working. | |||

The '''upper-right''' USB port seems to be only one USB EHCI debug port of the 4 available USB ports on the board. | |||

This can very easily be verified by following [[EHCI_Debug_Port#Finding_the_USB_debug_port|USB EHCI debug port detection]] procedure that has been customized for this board: | |||

# <code>sudo dmesg -c</code> | |||

# Plug a USB flash memory in the '''upper-right''' USB port. | |||

# Run <code>dmesg | tail -n 18 | grep ehci</code> | |||

== TODO == | == TODO == | ||

* | * As of >=r4362 all PCI and PCI-E slots should be initialized correct and work fine. In fact either one PCI or one PCI-E '''must''' work if you want to be able to use a screen via AGP, as there are no on-board VGA for this mainboard. For hardware rev.1 it would be nice to get further test results. | ||

* There is also still an issue with I2C, which causes X startup to be very slow. You can bypass this problem by adding | * There is also still an issue with I2C, which causes X startup to be very slow. You can bypass this problem by adding | ||

Option "NoDDC2" | Option "NoDDC2" | ||

:to your "Device" section. | :to your "Device" section. '''Update (14.9.2009)''': Is this a v1 specific problem? Is this problem maybe fixed with the IRQ-Fix patch? | ||

If you can help out with these issues, please join the [[Mailinglist|mailing list]] and let us know! | If you can help out with these issues, please join the [[Mailinglist|mailing list]] and let us know! | ||

==See also== | |||

* [[Gigabyte m57sli Vendor Cooperation Score]] | |||

{{GPL}} | {{GPL}} | ||

Latest revision as of 08:37, 30 August 2017

This is end of life hardware, if you wish to get one you probably have to buy them used. However, the unique with this board is that it has high Coreboot Vendor Cooperation Score (VCS) and ECC memory support that mainly are used for servers.

Which board do you have?

The GIGABYTE GA-M57SLI-S4 seems to exist in 3 versions according to the link in https://github.com/coreboot/coreboot/blob/master/src/mainboard/gigabyte/m57sli/board_info.txt.

revision 1.0, and 1.1, are supplied with PLCC32 (soldered BIOS) and revision 2.0 with single 8 pin SOIC (SPI). All board revisions have unpopulated secondary pads. For the PLCC32 versions, the procedure outlined below can be used to add a ROM socket.

|

|

There is a version with a PLCC socket for the BIOS chip (socketed BIOS), but this might be a pre-production board since nobody has so far (2007/03) confirmed the purchase of a GA-M57SLI-S4 board with socketed BIOS. The mainboard photo on the backside of the GA-M57SLI-S4 box shows a ROM socket too.

There are 2 recent legacy BIOS variants are (for fallback purposes):

- F15E

- F15E for GA-M57SLI-S4 (rev. 1.0) non AM3, plcc (fifth variant: socketed plcc, maybe on early sample board only)

- F15E for GA-M57SLI-S4 (rev. 1.1) non AM3, plcc (not flashable with legacy tool here (no 'chipset support')

- FHL for GA-M57SLI-S4 (rev. 2.0) AM3 ready, soic

Status

| Device/functionality | Status | Comments | ||||||

|---|---|---|---|---|---|---|---|---|

| CPU | ||||||||

| CPU works | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| L1 cache enabled | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| L2 cache enabled | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| L3 cache enabled | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Multiple CPU support | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Multi-core support | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| Hardware virtualization | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | tested with the kvm package of ubuntu 7.04 | ||||||

| RAM | ||||||||

| EDO | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| SDRAM | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| SO-DIMM | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| DDR | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| DDR2 | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| DDR3 | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Dual channel support | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | According to memtest86+ it works. | ||||||

| ECC support | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| On-board Hardware | ||||||||

| On-board IDE 3.5" | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| On-board IDE 2.5" | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board SATA | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | A FILO patch is needed (see below) as coreboot is too fast and the disks have not spun up yet when coreboot is done. | ||||||

| On-board SCSI | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board USB | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Tested: mounting USB storage devices and accessing files on them. USB MIDI-keyboard works, too (keyboard == the music instrument, in this case). | ||||||

| On-board VGA | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board Ethernet | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| On-board Audio | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Use modprobe snd-hda-intel (Alsa). | ||||||

| On-board Modem | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board FireWire | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Confirmed working as of r3023 - a firewire disk is detected and works fine. | ||||||

| On-board Smartcard reader | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board CompactFlash | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board PCMCIA | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board Wifi | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board Bluetooth | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| On-board SD card reader | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Add-on slots/cards | ||||||||

| ISA add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Audio/Modem-Riser (AMR/CNR) cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Works on hardware rev.2. Needs coreboot v2 >= r4362. Please do additional tests on hardware rev.1. | ||||||

| Mini-PCI add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Mini-PCI-Express add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Unknown | |||||||

| PCI-X add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| AGP graphics cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI Express x1 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Works on hardware rev.2. Needs coreboot v2 >= r4362. Please do additional tests on hardware rev.1. | ||||||

| PCI Express x2 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI Express x4 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI Express x8 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PCI Express x16 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Works on hardware rev.2. Needs coreboot v2 >= r4362. Please do additional tests on hardware rev.1. | ||||||

| PCI Express x32 add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| HTX add-on cards | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Legacy / Super I/O | ||||||||

| Floppy | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | Should work, but ***needs testing***. | ||||||

| Serial port 1 (COM1) | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Serial console for coreboot and Linux is fully operational. | ||||||

| Serial port 2 (COM2) | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Parallel port | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Works with a parallel port printer. (Needs coreboot v2 >= r4396.) | ||||||

| PS/2 keyboard | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Works on Seabios without problems. | ||||||

| PS/2 mouse | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| Game port | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Infrared | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| PC speaker | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Works with beep (use modprobe pcspkr). | ||||||

| DiskOnChip | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Input | ||||||||

| Trackpoint | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Touchpad | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Fn Hotkeys | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Fingerprint Reader | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Laptop | ||||||||

| Docking VGA | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Docking LAN | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Docking USB | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Docking Audio | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Docking Displayport | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Thinklight | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Webcam | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Miscellaneous | ||||||||

| Sensors / fan control | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Sensors and fans work, see instructions. Some sensor readouts are off, and the pwm polarity seems to be inverted, but fan speed can be set. | ||||||

| Hardware watchdog | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | modprobe it87_wdt | ||||||

| SMBus | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| CAN bus | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| CPU frequency scaling | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Needs coreboot v2 >= r4364. | ||||||

| Other powersaving features | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| ACPI | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Needs coreboot v2 >= r4364. | ||||||

| Reboot | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | |||||||

| Poweroff | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Needs coreboot v2 >= r4364. | ||||||

| Suspend | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Unknown | |||||||

| Nonstandard LEDs | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | HD-LED works. Power-LED untested. | ||||||

| High precision event timers (HPET) | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Needs coreboot v2 >= r4364. | ||||||

| Random number generator (RNG) | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | N/A | |||||||

| Wake on modem ring | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| Wake on LAN | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| Wake on keyboard | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| Wake on mouse | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Untested | |||||||

| TPM | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | Unknown | |||||||

| Flashrom | OK=lime | TODO=red | No=red | WIP=orange | Untested=yellow | N/A=lightgray | yellow }}" | OK | Use revision 3088 or higher. Flashrom now works on both the PLCC and SOIC/SPI versions of the board. | ||||||

Supported CPUs

Factory BIOS CPU support lists

Coreboot CPU support list

Initial socket CPUs are listed as they work with any factory BIOS version, are likely to work with Coreboot, are affordable, and AMD CPUs are sometimes unlocked in early editions. Also, if you plan to evaluate a series of CPUs, please think about buying a CPU cooler compatible for respectively sockets.

| Date | Mainboard | CPU | Coreboot | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | PCB | Backward compatibility and/or unique feature | CPUID signature | Family | Frequency | Processor name (BIOS) | Part number(s) | Introduction date | Socket(s) | Microarchitecture | Model | Stepping | TDP | Version | Git clone revision | Working with on-board VGA | Working with off-board VGA | Working overclocked (ACC) | ||

| 2015-01-29 | M57SLI-S4 | 2.0 | First choice CPU for Coreboot evaluation (if this one runs you can try other models): Boards lowest supported CPU (of all CPUs, K8 family, AM2 socket) | 40FF2 | AMD Sempron | 2800+ (rated) 1600 MHz (real) |

AMD Sempron(tm) Processor 2800+ | SDA2800IAA2CN is an OEM/tray microprocessor SDA2800CNBOX is a boxed microprocessor |

2006-05-23 | AM2 | K8/15 (0Fh) | 79 (04Fh) | F2 | 62W | 4.0-8014-g20c2c4b | 20c2c4b277e72c279229c1eea19aeaee94ab2ae1 | N/A | No | Untested | |

| - | M57SLI-S4 | 2.0 | Boards lowest supported CPU for K10.5 family, and AM2+ socket | 0F23h | AMD Athlon | 2400 MHz | AMD Athlon(tm) 7450 Dual-Core Processor | AD7450WCJ2BGH is an OEM/tray microprocessor | 2008-12-14 | AM2, AM2+ | K10.5/16 (010h) | 2 (02h) | B3 | 95W | 4.0-7922-g78c5d58 | 78c5d584a087265e44b076647db19efd4db4a7bb | N/A | Untested | - | |

| - | M57SLI-S4 | 2.0 | Boards lowest supported AM3 socket CPU | 100F62 | AMD Sempron | 2700 MHz | AMD Sempron(tm) 140 Processor | SDX140HBK13GQ is an OEM/tray microprocessor SDX140HBGQBOX is a boxed microprocessor |

2009-07-22 | AM2+, AM3 | K10.5/16 (010h) | 6 (06h) | C2 | 45W | 4.0-7922-g78c5d58 | 78c5d584a087265e44b076647db19efd4db4a7bb | N/A | Untested | - | |

| - | M57SLI-S4 | 2.0 | Boards only Opteron supported CPU. Note that the board also has ECC support; Opteron with ECC memory are used in servers. | 40F33 | AMD Second Generation Opteron | 1800 MHz | Dual-Core AMD Opteron(tm) Processor 1210 | OSA1210IAA6CZ is an OEM/tray microprocessor OSA1210CZBOX is a boxed microprocessor |

2006-08-15 | AM2 | K8/15 (0Fh) | 67 (043h) | F3 | 103W | 4.0-7922-g78c5d58 | 78c5d584a087265e44b076647db19efd4db4a7bb | N/A | Untested | - | |

| - | M57SLI-S4 | 2.0 | Boards lowest supported Phenom CPU | 100F23 | AMD Phenom X3 | 1900 MHz | AMD Phenom(tm) 8250e Triple-Core Processor | HD8250ODJ3BGH is an OEM/tray microprocessor HD8250ODGHBOX is a boxed microprocessor |

2008-09-08 | AM2+ / AM3 | K10.5/16 (010h) | 2 (02h) | B3 | 65W | 4.0-7922-g78c5d58 | 78c5d584a087265e44b076647db19efd4db4a7bb | N/A | Untested | - | |

| 2015-01-10 | M57SLI-S4 | 2.0 | - | 40F33 | AMD Athlon 64 X2 | 4600+ (rated) 2400 MHz (real) |

AMD Athlon(tm) 64 X2 Dual Core Processor 4600+ | ADO4600IAA5CZ is an OEM/tray microprocessor ADO4600CZBOX is a boxed microprocessor |

2006-05-23 | AM2 | K8/15 (0Fh) | 67 (043h) | F3 | 65W | 4.0-7922-g78c5d58 | 78c5d584a087265e44b076647db19efd4db4a7bb | N/A | No | Untested | |

- Motherboard

- Model: with lshw:

sudo lshw -short | grep bus

- Model: with lshw:

- CPU: Data used to figure out unique CPU in the CPUID database or factory BIOS supported CPUs. This is useful method to find out the CPU Part number(s) for an already running computer as it is written on the CPU normally blocked by a cooler.

- Family: With dmidecode:

sudo dmidecode -s processor-manufacturer && sudo dmidecode -s processor-family. In CPUID database search Family. - Introduction date: In CPUID database search Introduction date.

- Microarchitecture (CPU family, CPU architecture): In /proc/cpuinfo search cpu family. In CPUID database search Family.

- Frequency: With dmidecode:

sudo dmidecode | grep "Current Speed". In CPUID database search Frequency. - Processor name (BIOS) (CPU name string): In /proc/cpuinfo search model name. In CPUID database search Processor name (BIOS) or CPU name string.

- Socket (CPU socket): With dmidecode:

sudo dmidecode | grep Socket. In CPUID database search Socket. - Model: In /proc/cpuinfo search model. In CPUID database search Model.

- Vendor CPU Support List data. Used to alocate the CPU on their list.

- Stepping (Stepping level, CPU stepping): The term stepping level in the context of CPU architecture is a version/revision number. In Factory BIOS CPU support lists search Stepping. In /proc/cpuinfo search stepping. In CPUID database search Core stepping.

- TDP (Thermal Design Power, Wattage): In Factory BIOS CPU support lists search Wattage. In CPUID database search Watt.

- Family: With dmidecode:

- Factory BIOS

- Version: With dmidecode:

sudo dmidecode -s bios-version

- Version: With dmidecode:

- Coreboot

- Version:

git describe --tags - Git clone revision:

git log -1 --format=%H - Working overclocked (ACC): Advanced clock calibration (ACC) is a feature originally available for Phenom families of processors, particularly for Black Edition ones, to increase the overclocking potential of the CPU. ACC is supported by the SB710 and the SB750 southbridges, and available through BIOS settings on some motherboards. (Disclaimer - overclocking may damage your CPU. Damage, caused by overclocking, is not covered by CPU warranty.) See AMDGeeks Overclock database for CPUs.

- Version:

Before you begin

The fact that the BIOS is soldered onto the board complicates matters considerably, because it means that one flash of a faulty image will render your board unusable (it will be 'bricked'). Top Hat Flash does not work with the SST 49LF040B 33-4C-NHE soldered onto the GA-M57SLI-S4, but might work with other chips (FWH). This means a hardware hack is necessary to prevent accidental bricking of the board.

With it's standard F8 legacy BIOS it requires the noapic boot parameter with most old kernels (legacy BIOS v. F12 is better).

sudo flashrom -p internal -w Coreboot_4.0-8014-g20c2c4b--Mainboard--Vendor_GIGABYTE._Model_GA-M57SLI-S4._ROM_chip_size_2048KB.rom [...] Error: Image size doesn't match) if the size of the hardware chip mismatch the Coreboot image configured ROM chip size. This is a good thing as it will save you from accidentally burning Cooreboot to the primary chip if you forget to toggle the hardware switch to the secondary chip. Chips with equal size will likely make you break the board one day. You have been warned!Hardware hack

PLCC32

If you have a PLCC32 revision, it is possible to desolder the BIOS chip, and replace it with a PLCC socket. You will need some tools (heat gun/pencil, good soldering iron, etc) and soldering experience to do that. The other option is to add a PLCC socket to the empty position next to the soldered-on BIOS chip. With an extra resistor and a switch, this allows switching between 2 BIOS chips. This has been documented carefully by ST; see his instructions.

If you don't feel like doing this yourself, you could try to find a commercial service to do it for you. One way to find a shop is to look for game console modification shops, they do this sort of thing (and more advanced things) all day and should be able to help you for around $50 if you bring the needed components (PLCC socket, resistor, wire and switch). Possibly a friendly TV or radio repair shop could help too, but they may not have suitable soldering equipment for the surface mount parts.

Once you put a socket on the board, you will also discover that the RD1-PMC4 BiosSavior does not work with this motherboard: the RD1's built-in chip seems to be incompatible with the mainboard. This means you will need to hot-swap BIOS chips until you have a working coreboot chip. Plugging your BIOS chip into the RD1 and switching it to 'ORG' does work though. I have used the BiosSavior to ease hot swapping; it's a lot easier to pull out the BiosSavior and replace the chip plugged into it than to replace the ROM chip on the board.

This is the list of BiosSavior resellers: IOSS. In the US, FrozenCPU seems to have stock (verified 2007/04). Eksitdata in Sweden also seems to have stock (verified 2007/03).

SOIC (SPI)

If you have an SOIC revision, you can add a second SOIC chip in the unpopulated position, and use a switch to toggle between both chips.

The most recent instructions by Peter Stuge can be found here [1]. This is the recommended modification. Peter's company also sells pre-modified boards if you don't want to do the soldering, contact peter at stuge dot se for more information. Also, you may watch Peter's video lecture on coreboot available at youtube asf. for recent info.

Older instructions can be found here here, and here are some photos. These instructions have been confirmed to work.

It's also possible to put a SOIC socket on the second pad, as documented by Harald Gutmann, with pictures here and here.

Here's are a few pictures of a completed modification using the older instructions:

|

|

Flashrom

PLCC32 chips

Flashrom works fine both under the proprietary BIOS and coreboot. Use revision 3088 or higher.

SOIC (SPI) chips

Flashrom works well on the SOIC version of the board and can detect various SPI chips, including the factory soldered MX25L4005.

Payload

Coreboot requires a payload to boot an operating system.

If you want to boot from the network, you will need to use Etherboot.

If you want to boot from an IDE drive, SATA drive, USB stick or CDROM, you can use FILO.

Another possible payload is 'linux-as-a-bootloader' (LAB). You will need a 1MB ROM chip (the GA-M57SLI-S4 comes with a 512KB ROM chip) for this payload. It consists of a (stripped down) kernel + busybox, which can then be used to kexec a kernel from disk. If your disks are playing up, you will still have a busybox environment on boot, which could be useful for debugging.

Buildrom vs. manual build

You can build a coreboot image with a kconfig-style configuration tool (buildrom) if you want to use FILO or LAB. This is by far the easiest way to build a ROM image. Continue to the Buildrom section.

If you want another payload or would like to get closer to the metal, you can use the manual build method outlined below under Manual build.

Buildrom

Skip this section if you want to do a manual build; in that case jump to Manual build below.

Check out buildrom:

svn co svn://coreboot.org/buildrom

Now configure buildrom:

cd buildrom/buildrom-devel make menuconfig

Configure to your liking. If you use the LAB payload, make sure to exclude the kexec binary and boot menu from the initramfs, otherwise your image will be too big. Please note that currently only the FILO and LAB payloads have been tested. The other payloads likely require some more work before they will be useable. Patches are welcome, of course.

make

If all goes well, you should now have a ROM image file

deploy/gigabyte-m57sli.rom

If you are building a FILO payload, it will be exactly 512KB in size. If you are building an LAB payload, the image will be 1MB.

FILO payload

Skip this section if you use the LAB payload.

When using FILO in GRUB emulation mode, it's important to get a few details right in your GRUB boot stanza. This is what mine looks like:

title Ubuntu LB, kernel 2.6.21-rc3 root (hd4,0) kernel /boot/vmlinuz-2.6.21-rc3 root=/dev/sda1 ro acpi_use_timer_override console=tty0 console=ttyS0,115200 savedefault boot

Note the root device - FILO sees the first SATA device as hd4.

In order to get serial output from GRUB, you will also need to add something like this to your menu.lst:

# serial port 0 serial --unit=0 --speed=115200 terminal --timeout=15 serial console

LAB payload

Skip this section if you use the FILO payload.

The LAB payload expects a file /lab.conf on /dev/sda1 with contents like this:

CMDLINE="root=/dev/sda1 ro console=tty0 console=ttyS0,115200" KERNEL="/vmlinuz-2.6.22.1" INITRD="" VT="1"

This is the kernel that you will be running after boot. It will be kexec'ed by the kernel that is burned into your ROM chip.

You will also need a statically linked copy of kexec, which the LAB payload expects to reside at

/kexec on /dev/sda1

If you are on Ubuntu, you can easily recompile your kexec package to be statically linked by following these instructions:

cd /usr/src apt-get source kexec-tools export LDFLAGS="-static"

Now edit kexec-tools-1.101-kdump10/kexec-tools-1.101/kexec/Makefile, change line 53 to

$(CC) $(LDFLAGS) $(KCFLAGS) -o $@ $(KEXEC_OBJS) $(UTIL_LIB) $(LIBS)

(you're adding the LDFLAGS variable)

cd kexec-tools-1.101-kdump10 dpkg-buildpackage -rfakeroot -b cd .. dpkg -i kexec-tools_1.101-kdump10-2ubuntu2_i386.deb

Adjust the package name as necessary for your distribution.

If you want to build the latest kexec from Debian Sid, you're going to need to be a little more careful. Set -static:

export LDFLAGS="-static"

Then build the package

apt-get source kexec-tools -b

This will fail more or less like this

$ gcc -static -lz -o build/sbin/kexec kexec/kexec.o kexec/ifdown.o kexec/kexec-elf.o kexec/kexec-elf-exec.o kexec/kexec-elf-core.o kexec/kexec-elf-rel.o kexec/kexec- elf-boot.o kexec/kexec-iomem.o kexec/crashdump.o kexec/crashdump-xen.o kexec/arch/i386/kexec-x86.o kexec/arch/i386/kexec-elf-x86.o kexec/arch/i386/kexec-elf-rel-x86.o kexec/arch/i386/kexec-bzImage.o kexec/arch/i386/kexec-multiboot-x86.o kexec/arch/i386/kexec-beoboot-x86.o kexec/arch/i386/kexec-nbi.o kexec/arch/i386/x86-linux-setup.o kexec/arch/i386/crashdump-x86.o kexec/purgatory.o libutil.a kexec/kexec.o: In function `slurp_decompress_file': /usr/src/kexec-tools-20080324/kexec/kexec.c:503: undefined reference to `gzopen' /usr/src/kexec-tools-20080324/kexec/kexec.c:519: undefined reference to `gzread' /usr/src/kexec-tools-20080324/kexec/kexec.c:533: undefined reference to `gzclose' /usr/src/kexec-tools-20080324/kexec/kexec.c:524: undefined reference to `gzerror' /usr/src/kexec-tools-20080324/kexec/kexec.c:535: undefined reference to `gzerror' /usr/src/kexec-tools-20080324/kexec/kexec.c:505: undefined reference to `gzerror' collect2: ld returned 1 exit status

The problem is that the -lz really needs to go at the end of the gcc command line - otherwise it gets filtered out by gcc. When it encounters -lz, it has not yet seen any need for the libz library so it automatically removes it. Manually running

gcc -static -o build/sbin/kexec kexec/kexec.o kexec/ifdown.o kexec/kexec-elf.o kexec/kexec-elf-exec.o kexec/kexec-elf-core.o kexec/kexec-elf-rel.o kexec/kexec-elf-boot.o kexec/kexec-iomem.o kexec/crashdump.o kexec/crashdump-xen.o kexec/arch/i386/kexec-x86.o kexec/arch/i386/kexec-elf-x86.o kexec/arch/i386/kexec-elf-rel-x86.o kexec/arch/i386/kexec-bzImage.o kexec/arch/i386/kexec-multiboot-x86.o kexec/arch/i386/kexec-beoboot-x86.o kexec/arch/i386/kexec-nbi.o kexec/arch/i386/x86-linux-setup.o kexec/arch/i386/crashdump-x86.o kexec/purgatory.o libutil.a -lz

fixes the problem and gives you a static copy of kexec in build/sbin/kexec.

You can tell if your copy of kexec is statically linked by running 'file' on it:

file /sbin/kexec

If all is well, you will see something like this:

/sbin/kexec: ELF 32-bit LSB executable, Intel 80386, version 1 (SYSV), for GNU/Linux 2.2.0, statically linked, for GNU/Linux 2.2.0, stripped

The binary will also be considerably larger than its dynamically linked cousin.

Note that you must build a 32-bit version of kexec, because buildrom puts a 32 bit kernel into the ROM image. A 32-bit kexec can kexec into a 64 bit kernel, so if your system is 64 bit this will work just fine.

The LAB code currently expects lab.conf and kexec to live in / on /dev/sda1.

Manual build

Skip this section if you used buildrom; in that case jump to Burning coreboot below.

Building the payload

In order to boot from a SATA disk, we use FILO.

Once you've downloaded FILO, you will need to put a file 'Config' in its root tree. An example can be found in the distribution, called 'defconfig'.

You can configure FILO to load GRUB. Here's my Config, which does that:

# Use grub instead of autoboot? USE_GRUB = 1 # Grub menu.lst path MENULST_FILE = "hde1:/grub/menu.lst" # Driver for hard disk, CompactFlash, and CD-ROM on IDE bus IDE_DISK = 1 # Add a short delay when polling status registers # (required on some broken SATA controllers) IDE_DISK_POLL_DELAY = 1 # Driver for USB Storage USB_DISK = 1 # VGA text console VGA_CONSOLE = 1 PC_KEYBOARD = 1 # Enable the serial console SERIAL_CONSOLE = 1 # Serial console; real external serial port SERIAL_IOBASE = 0x3f8 SERIAL_SPEED = 115200 # Filesystems FSYS_EXT2FS = 1 FSYS_ISO9660 = 1 # Support for boot disk image in bootable CD-ROM (El Torito) ELTORITO = 1 # PCI support SUPPORT_PCI = 1 # Enable this to scan PCI busses above bus 0 # AMD64 based boards do need this. PCI_BRUTE_SCAN = 1 # Loader for standard Linux kernel image, a.k.a. /vmlinuz LINUX_LOADER = 1

Because physical disks take a while to spin up, I've had to add an extra delay to FILO:

Index: main/filo.c

===================================================================

--- main/filo.c (revision 34)

+++ main/filo.c (working copy)

@@ -60,6 +60,7 @@

/* Initialize */

init();

+ delay(5);

grub_main();

return 0;

}

This will make FILO wait 5 seconds before probing the disks, making sure that the SATA disk is ready.

In order to get serial output from GRUB, you will also need to add something like this to your menu.lst:

# serial port 0 serial --unit=0 --speed=115200 terminal --timeout=15 serial console

Now execute 'make', which will generate a filo.elf file that will be your payload. You will need to refer to this file to build coreboot as explained below, because it gets included in the coreboot ROM image.

When using FILO in GRUB emulation mode, it's important to get a few details right in your GRUB boot stanza. This is what mine looks like:

title Ubuntu LB, kernel 2.6.21-rc3 root (hd4,0) kernel /boot/vmlinuz-2.6.21-rc3 root=/dev/sda1 ro acpi_use_timer_override console=tty0 console=ttyS0,115200 savedefault boot

Note the root device - FILO sees the first SATA device as hd4.

Also, the GA-M57SLI-S4 will not boot unless you add acpi_use_timer_override as a kernel option - and use a modern kernel (tested on 2.6.20.1 and up). Hopefully this will be fixed in newer kernels. If you have a somewhat older kernel (tested with 2.6.16 and up), add these options: apic=debug acpi_dbg_level=0xffffffff pci=noacpi,routeirq snd-hda-intel.enable_msi=1.

Building coreboot

See the Build HOWTO for information on how to build coreboot for this board.

Burning coreboot

Make SURE that you have a fallback position: a ROM chip with backup copy of your factory ROM image (you can make one with flashrom), and either a socket on the board to plug the backup chip into, or the tools and skills to remove a 'bricked' BIOS chip from the board and replace it with a socket for the backup chip.

If you do not prepare properly, you are likely to brick your motherboard. You have been warned!

You can use flashrom to write the image:

flashrom -p internal -w coreboot.rom

(that's assuming the image is called coreboot.rom).

Debugging Coreboot execution

See EHCI Debug Port for USB debug hardwares that you need to use with the USB debug port.

USB debug port

sudo lshw # gives one result for EHCI capable USB port.

*-usb:1

description: USB controller

product: MCP55 USB Controller

vendor: NVIDIA Corporation

physical id: 2.1

bus info: pci@0000:00:02.1

version: a2

width: 32 bits

clock: 66MHz

capabilities: debug pm ehci bus_master cap_list

configuration: driver=ehci_hcd latency=0 maxlatency=1 mingnt=3

resources: irq:22 memory:ee204000-ee2040ff

lspci

00:02.1 USB controller: NVIDIA Corporation MCP55 USB Controller (rev a2)

lspci -v | grep ehci

Kernel driver in use: ehci_hcd

lspci -v

00:02.1 USB controller: NVIDIA Corporation MCP55 USB Controller (rev a2) (prog-if 20 [EHCI])

Subsystem: Gigabyte Technology Co., Ltd Device 5004

Flags: bus master, 66MHz, fast devsel, latency 0, IRQ 22

Memory at ee204000 (32-bit, non-prefetchable) [size=256]

Capabilities: <access denied>

Kernel driver in use: ehci_hcd

lspci -nnk | grep 10de:036d

00:02.1 USB controller [0c03]: NVIDIA Corporation MCP55 USB Controller [10de:036d] (rev a2)

10de:036d is found on the list of controllers verified to have the debug port capability so we know that it is working.

The upper-right USB port seems to be only one USB EHCI debug port of the 4 available USB ports on the board.

This can very easily be verified by following USB EHCI debug port detection procedure that has been customized for this board:

sudo dmesg -c- Plug a USB flash memory in the upper-right USB port.

- Run

dmesg | tail -n 18 | grep ehci

TODO

- As of >=r4362 all PCI and PCI-E slots should be initialized correct and work fine. In fact either one PCI or one PCI-E must work if you want to be able to use a screen via AGP, as there are no on-board VGA for this mainboard. For hardware rev.1 it would be nice to get further test results.

- There is also still an issue with I2C, which causes X startup to be very slow. You can bypass this problem by adding

Option "NoDDC2"

- to your "Device" section. Update (14.9.2009): Is this a v1 specific problem? Is this problem maybe fixed with the IRQ-Fix patch?

If you can help out with these issues, please join the mailing list and let us know!

See also

|

This work is free software; you can redistribute it and/or modify it under the terms of the GNU General Public License as published by the Free Software Foundation; either version 2 of the License, or any later version. This work is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU General Public License for more details. |